# Full Range Neutral-Point Voltage Balancing for Four-Level $\pi$ Type Inverter Using Carrier-Overlapped PWM

Tan Luong Van<sup>1,\*</sup> and Ngo Ly Dang<sup>1</sup>

# ARTICLE INFO

Article history:

Received: 6 August 2024 Revised: 15 October 2024 Accepted: 16 May 2025 Online: 31 October 2025

Keywords: Four-level π-Type Neutral-point voltage balance Carrier-overlapped PWM

#### ABSTRACT

Four-level  $\pi$ -type inverters face a major issue with neutral-point voltage imbalance, which prevents their widespread industrial application. This paper proposes a solution to this issue using carrier-overlapped pulse width technique. Three DC-link capacitors can be maintained at the rated value under ideal operating scenarios. However, to address voltage deviations caused by nonideal factors, the middle DC-link capacitor voltage is balanced by adjusting the duty cycles of switching signals, while the upper and lower DC-link capacitor voltages are balanced using zero-sequence voltage injection. Finally, to validate the feasibility of the modulation technique and voltage controllers, simulation results from the 3 kVA inverter prototype have been incorporated.

## 1. INTRODUCTION

In applications requiring high power and medium voltage (3–33 kV), multilevel inverters (MLIs) are an attractive solution due to their significant benefits over two-level inverters [1-3]. Recently, MLIs have become more appealing to researchers in low power applications due to their ability to improve power quality and power density, lower EMI, and provide a wide range of DC link voltages [4-6]. Several conventional MLIs, including the cascaded Hbridge (CHB) inverter, the neutral-point clamped (NPC) inverter, the flying capacitor (FC) inverter, and the modular multilevel inverter (MMC), have been successfully implemented in industry [5-7]. However, more power semiconductors and passive components are needed for MLIs with higher voltage levels, such as four or five levels, which increases the complexity of the circuit and control (modulation, capacitor voltage balancing, etc.).

In [8], a four-level  $\pi$ -type inverter was introduced, offering significant advantages, including reduced complexity and fewer components compared to other multilevel inverters. It eliminates the need for clamping diodes or flying capacitors and uses only six switching devices per phase leg, leading to simpler circuitry and lower total conduction losses. These features make it particularly suitable for high-density, low-voltage applications like electric vehicle systems and aircraft applications. Nevertheless, a major issue with the four-level  $\pi$ -type inverter is the capacitor voltage imbalance caused by having multiple clamping points in the DC-link, similar to the NPC circuit [8], [9].

In [10], the DC-link capacitor voltages can be balanced

under certain operating conditions by injecting zero-sequence voltage (ZSV) into the reference voltages. For space-vector modulation (SVM), voltage balance cannot be achieved for the capacitor voltages under specific operating situations that exceed the theoretical boundary when using the nearest-three-vectors (NTV) technique[11]. Hardware solutions can overcome theoretical restrictions and improve the ability to balance capacitor voltages by configuring two converters to be coupled back-to-back [12], [13] or by using auxiliary balancing circuit [14], [15]. Nevertheless, these techniques require additional hardware, which increases the cost and complexity of the system.

To maintain capacitor voltage balance across all operating regions without the need for additional circuits, the carrier-overlapped pulse width modulation (COPWM) method, originally developed for NPC prototypes [16], [17], is applied to the 4L  $\pi$ -type inverter. COPWM is a novel modulation technique that overlays multiple carrier signals to generate more voltage levels in a sampling period. This scheme offers greater flexibility in achieving various control objectives, such as maintaining capacitor voltage balance.

Under this modulation method, the DC-link capacitors naturally achieve voltage balance under ideal conditions. However, to mitigate voltage deviations caused by non-ideal factors, a capacitor voltage control strategy should be developed. This is achieved through ZSV injection technique, which balances the voltage of the outer DC-link capacitors, and by modifying the duty ratios of switches to regulate the voltage of the middle DC-link capacitor. Simulation studies have validated the effectiveness of the

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Electronic Engineering, Ho Chi Minh city University of Industry and Trade, Ho Chi Minh, 760310, Vietnam.

<sup>\*</sup>Corresponding author: Tan Luong Van; Phone: +84-909-653-157; Email: luongvt@huit.edu.vn.

COPWM method in the 4L  $\pi$ -type inverter under various operating conditions.

The proposed COPWM scheme for the 4L  $\pi$ -type inverter offers the following advantages:

- Maintains balanced capacitor voltages regardless of modulation index or load power factor.

- Eliminates the need for auxiliary balancing circuits.

- Enables easy implementation on any microcontroller, as COPWM is based on a level-shifted PWM scheme.

# 2. PWM MODULATION AND DC-LINK CAPACITOR VOLTAGE BALANCING CONTROL

# 2.1. Circuit configuration and switching states

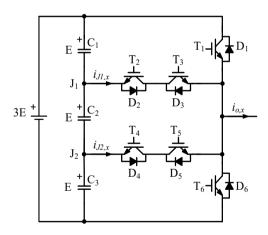

The configuration of the phase leg for the four-level  $\pi$ -Type inverter is illustrated in Fig. 1, comprising six switching devices from  $T_1$  to  $T_5$ . It should be noted that  $T_1 - T_2$ ,  $T_3 - T_4$ , and  $T_5 - T_6$  are operated in complementary pairs. Table 1 lists the switching states, with E being the nominal voltage of the three DC-link capacitors. In the DC-Link, there are two junctions, N1 and N2. The junction currents flowing from these points, labeled as  $i_{J1,x}$  and  $i_{J2,x}$ , are determined by the phase load current,  $i_{o,x}$ , along with the switching states, subscript symbol x denotes phase a, b, or c.

Fig. 1. Single phase circuit of 4L  $\pi$ -Type inverter.

Table 1. Switching states of 4L  $\pi$ -Type inverter

| T <sub>1</sub> &<br>T <sub>2</sub> | T3&<br>T4 | T <sub>5</sub> &<br>T <sub>6</sub> | Switching states | Vox | <b>i</b> J1,x | <i>i</i> <sub>J2,x</sub> |

|------------------------------------|-----------|------------------------------------|------------------|-----|---------------|--------------------------|

| 1                                  | 1         | 1                                  | $V_3$            | 3E  | -             | 1                        |

| 0                                  | 1         | 1                                  | $V_2$            | 2E  | $i_{0,x}$     | -                        |

| 0                                  | 0         | 1                                  | $V_1$            | Е   | -             | $i_{0,x}$                |

| 0                                  | 0         | 0                                  | $V_0$            | 0   | -             | -                        |

#### 2.2. COPWM Modulation

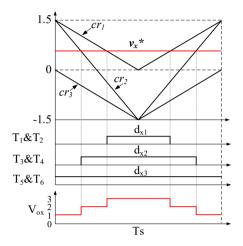

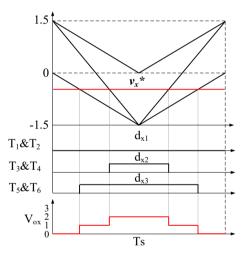

Fig. 2 displays a diagram of the COPWM approach for the

4L inverter. Carrier  $Cr_2$  overlaps both  $Cr_1$  and  $Cr_3$  with a peak-to-peak value of 3, while carriers  $Cr_1$  and  $Cr_3$  are level shifted, with  $Cr_1$  put in the positive voltage zone and  $Cr_3$  in the negative voltage region.

## (a) Positive reference voltage

(b) Negative reference voltage

Fig. 2. COPWM modulation scheme for 4L  $\pi$ -Type.

The duty cycles generated by these carriers can be represented as functions of the phase reference voltage using this COPWM approach as follows:

1) When the reference voltage  $v^*$  is positive and intersects carriers  $Cr_1$  and  $Cr_2$ :

$$d_{x1} = 2/3 \cdot v_x^*; d_{x2} = 1/3 \cdot (v_x^* + 1.5); d_{x3} = 1.$$

(1)

2) When the reference voltage  $v^*$  is negative and intersects carriers  $Cr_2$  and  $Cr_3$ :

$$d_{x1} = 0; d_{x2} = 1/3 \cdot (v_x^* + 1.5); d_{x3} = 2/3 \cdot (v_x^* + 1.5).$$

(2)

According to Table 1, the junction current at N1 corresponds to the phase load current when the pole voltage is 2E, and the junction current at N2 corresponds to the phase load current when the voltage level is E. Referring to

Fig. 2, the following can be used to express the single-phase junction currents throughout a sampling period:

$$I_{J_{1,x}} = d_{x2} - d_{x1} = \begin{cases} 1/3 \cdot \left(-v_x^* + 1.5\right) \cdot i_{0,x} & 0 \le v_x^* \le 1.5\\ 1/3 \cdot \left(v_x^* + 1.5\right) \cdot i_{0,x} & -1.5 \le v_x^* \le 0 \end{cases}$$

(3)

$$I_{J2,x} = d_{x3} - d_{x2} = \begin{cases} 1/3 \cdot \left(-v_x^* + 1.5\right) \cdot i_{0,x} & 0 \le v_x^* \le 1.5\\ 1/3 \cdot \left(v_x^* + 1.5\right) \cdot i_{0,x} & -1.5 \le v_x^* \le 0 \end{cases}$$

(4)

Assuming the capacitance of the DC-link capacitors is the same, denoted as  $C_0$ , the voltage errors of these capacitors caused by single phase junction currents in a carrier period can be expressed as follows:

$$\Delta v_{C1,x} = \frac{1}{3C_0} \left( 2I_{J1,x} + I_{J2,x} \right) T_s \tag{5}$$

$$\Delta v_{C2,x} = -\frac{1}{3C_0} \left( I_{J1,x} - I_{J2,x} \right) T_s \tag{6}$$

$$\Delta v_{C3,x} = \frac{1}{3C_0} \left( -I_{J1,x} - 2I_{J2,x} \right) T_s \tag{7}$$

Under ideal and constant conditions, the middle DC-Link capacitor voltage can maintain balance in a carrier period since the difference between the two junction currents, as determined by formulas (3) and (4), is zero. According to (5) and (7), the voltage difference between the top and bottom capacitors caused by a phase leg depends on the total of two junction currents, which can be expressed as follows:

$$\Delta v_{C1,x} - \Delta v_{C3x} = \frac{1}{C_0} \left( I_{J1,x} + I_{J2,x} \right) T_s \tag{8}$$

The total junction current can be derived from (3) and (4):

$$I_{J_{1-2,x}} = I_{J_{1,x}} + I_{J_{2,x}} = \begin{cases} 2/3 \cdot \left(-v_x^* + 1.5\right) \cdot i_{0,x} & 0 \le v_x^* \le 1.5\\ 2/3 \cdot \left(v_x^* + 1.5\right) \cdot i_{0,x} & -1.5 \le v_x^* \le 0 \end{cases}$$

(9)

In the fundamental period, assuming that the reference voltage and load current are sinusoidal and symmetrical, the total junction current is zero. It has been demonstrated that, under ideal conditions, The top and bottom capacitors' natural voltage balance can be achieved via the COPWM, with the same outcomes attained for NPC [16].

#### 2.3. Capacitor Voltage Balancing Control

Under ideal conditions, COPWM can naturally balance the voltages of the DC-link capacitors; but, if it is not properly controlled in nonideal or dynamic scenarios, it may become unstable. Therefore, to efficiently maintain the capacitor voltages, a capacitor voltage controller has been developed.

According to (8), to reduce the voltage variation of the top and bottom capacitors during a sampling interval, a

reference value of total junction crrent needs to be injected into N1 and N2. This can be expressed as follows:

$$I_{J,ref} = -\frac{C_0 \cdot (v_{C1} - v_{C3})}{T_s} \tag{10}$$

Since the total junction current depends on the reference voltage, the conventional ZSV injection method can modify the reference signal shape, thereby altering the junction current. However, calculating the optimal ZSV needed to produce the exact directly total junction current is challenging. For simplicity, only five key zero-sequence voltages (ZSVs) are considered, which clamp any reference voltage to -1.5, 0, or 1.5, and are denoted as uz[j] (where j ranges from 0 to 5).

$$uz[0] = 0; uz[1] = 3 - v_{\text{max}}^*; uz[2] = 1.5 - v_{\text{max}}^*$$

$$uz[3] = 1.5 - v_{\text{mid}}^*; uz[4] = 1.5 - v_{\text{min}}^*; uz[5] = 0 - v_{\text{min}}^*$$

(11)

where,  $v_{\text{max}}^*$ ,  $v_{\text{mid}}^*$ , and  $v_{\text{min}}^*$  are the initial three-phase reference voltages' maximum, median, and maximal values. After injecting ZSVs, the changed reference voltage is described as follows:

$$v_{x,\text{mod}}^* \left[ j \right] = v_x^* + uz \left[ j \right] \tag{12}$$

Next, by using equation (9), the corresponding total junction currents for these important ZSVs are determined. and compared with the required value. The most appropriate ZSV is determined by selecting the one that produces the total junction current in that is closest to the needed current in (10). To prevent overmodulation, the limit for ZSVs can be determined:

$$\begin{cases} u_{z \max} = 1.5 - v_{\max}^* \\ u_{z \min} = -1.5 - v_{\min}^* \end{cases}$$

(11)

As previously mentioned, the difference between the two junction currents affects the middle DC-Link capacitor voltage, which can be expressed as follows:

$$I_{J1,x} - I_{J2,x} = \left(-d_{x1} + 2d_{x2} - d_{x3}\right) \cdot i_{o,x} \tag{12}$$

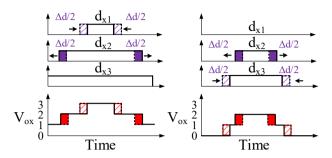

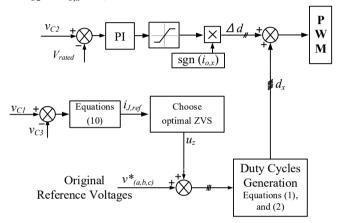

If there is a voltage variation in the capacitor C2, the duty cycles of the switching signal  $d_{x1}$ ,  $d_{x2}$ , and  $d_{x3}$  can be slightly adjusted to achieve voltage balancing under COPWM. A PI regulator takes  $\Delta v_{C2}$  to produce a duty ratio offset  $\Delta d$ . Consider the scenario where  $\Delta v_{C2}$  and  $i_{o,x}$  are positive: the difference between the two junction currents must be positive to discharge the capacitor. If the reference voltage is positive,  $\Delta d$  be added to  $d_{x2}$  and subtracted from  $d_{x1}$ . Conversely, if the reference voltage is negative,  $\Delta d$  be added to  $d_{x2}$  and subtracted from  $d_{x3}$ . The generated voltage changes after adjusting duty cycles are illustrated in Fig. 3. The block diagram for capacitor voltage control is depicted

in Fig. 4.

Fig. 3. Middle dc-link capacitor voltage balance method where  $\Delta v_{C2}$  and  $i_{o,x}$  are positive.

Fig. 4. Capacitor voltage control block diagram.

# 3. SIMULATION RESULTS

The performance of both the voltage balancing control and the PWM approach is demonstrated by the simulation results. The inverter parameters for the simulation are provided in Table 2.

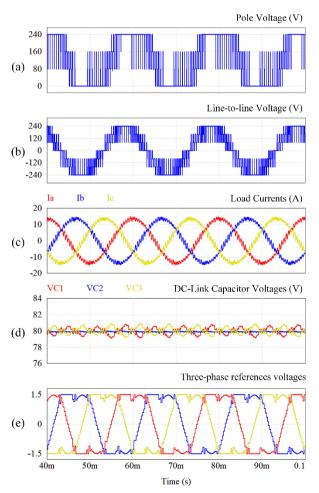

Fig. 5 illustrates the steady-state performance of the inverter with a high-power factor *R-L* load, showing a power factor (PF) of 0.998 at a unity modulation index, as specified in the parameters table. The pole voltage, line-to-line voltage, load currents are shown in Fig. 5(a), (b), and (c), respectively. As depicted in Fig. 5d, the three DC-link capacitor voltages remained well-balanced under high power factor and high modulation index conditions. In contrast, with the traditional PWM method, voltage balance cannot be maintained for high power factors when the modulation index exceeds 0.55 [10]. The modified reference voltages after adding ZSV component are shown in Fig. 5e.

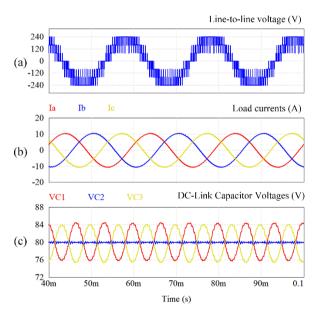

The steady-state performance of the inverter under a purely inductance load with m = 1.0 ( $R = 0 \Omega$ , L = 30 mH) is displayed in Fig. 6. The results of the simulation demonstrate that voltages in all capacitors can be well controlled at both low- and high-power factors.

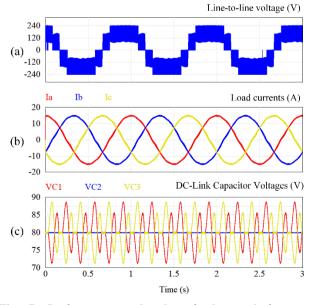

Furthermore, Fig. 7 displays the steady-state simulation result at the fundamental frequency of 1 Hz with a unity modulation index to demonstrate how well voltage

balancing works in the case of low fundamental frequency. The capacitor voltage  $V_{c2}$  remained well-balanced at the rated value, while the top and bottom capacitors experienced larger voltage fluctuations. However, the voltage ripple in two capacitors is still within acceptable range ( $\pm 10\%$ ).

Table 2. Circuit parameters for the simulation

| Parameters            | Symbols     | Values     |  |

|-----------------------|-------------|------------|--|

| Power rating          | $S_{rated}$ | 3 kVA      |  |

| DC source voltage     | $V_{dc}$    | 240 V      |  |

| Line-to-line voltage  | $V_{l-l}$   | 170V       |  |

| Fundamental frequency | $f_o$       | 50 Hz      |  |

| DC-Link capacitor     | $C_0$       | 2 mF       |  |

| Carrier frequency     | $f_{sw}$    | 2 kHz      |  |

| R-L Load              |             | 10 Ω, 2 mH |  |

Fig. 5. Performance under high power factor and unity modulation index condition (m = 1.0, PF = 0.998).

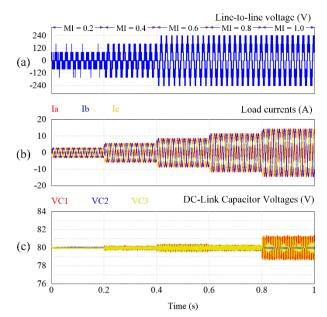

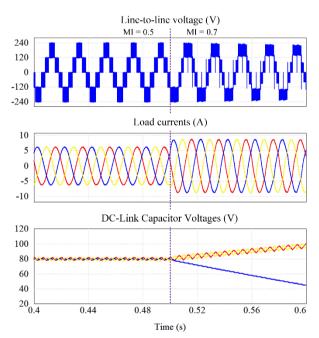

The PWM method and voltage controllers have been verified in various dynamic conditions. Fig. 8 shows the simulation results when the modulation index changes in 0.2 steps, increasing from 0.2 to 1.0. The waveforms of the line-to-line voltage, phase currents, and DC-link capacitor voltages under LSPWM with modulation indices of m = 0.5 and m = 0.7 are displayed in Figs. 9 to confirm the performance of the COPWM in comparison to the conventional LS PWM. At a modulation index of 0.5, the LSPWM and zero-sequence-voltage injection method effectively equalizes the three DC-link capacitor voltages. However, increasing the modulation index to 0.7 disrupts this balance.

Fig. 6. Performance under pure inductance load and unity modulation index condition.

Fig. 7. Performance under low fundamental frequency operation.

Fig. 8. Performance under a step change in modulation index.

Fig. 9 Performance under LSPWM for a step change in modulation index (0.5 to 0.7).

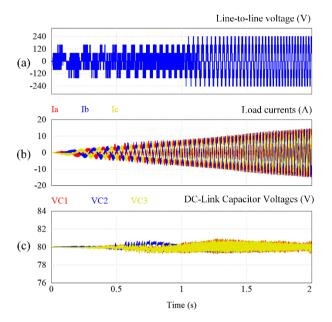

The performance under variable voltage variable frequency (VVVF) is illustrated in Fig. 10. In two seconds, the modulation index increases uniformly from 0 to 1, while the fundamental frequency increases correspondingly from 0 to 50 Hz. It is evident that the three capacitor voltages can be maintained throughout the entire modulation index range.

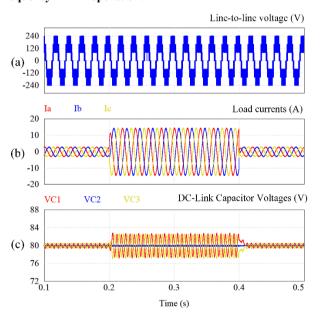

The performance of the inverter has been tested under step load conditions while operating at 50 Hz fundamental frequency and unity modulation index. Initially, the 4L  $\pi$ -type is operated around 20% rated power and then, the load is changed to the rated value at t = 0.2 s. At t = 0.4 s, the load

steps down from full load back to 20 %. As shown in Fig. 11, in both cases, the maximum deviation voltage of DC-link capacitors during the transient period is approximately 5 % of the nominal voltage (4 V).

Fig. 10. Performance under variable voltage variable frequency VVVF operation.

Fig. 11. Performance at the transient load condition.

#### 4. CONCLUSIONS

Originally developed for NPC prototypes, COPWM has been successfully applied to the  $4L \pi$ -type inverter, offering greater flexibility in achieving various control objectives, such as maintaining capacitor voltage balance. Under PWM control, natural voltage balancing of all DC-link capacitors is achieved under ideal steady-state conditions. However, to

address voltage deviations caused by nonideal factors, a capacitor voltage control strategy is employed. This strategy involves zero-sequence voltage injection to balance the upper and lower DC-link capacitor voltages and adjusting the duty cycles of switching signals to balance the central DC-link capacitor voltage. The effectiveness of the COPWM method in the 4L  $\pi$ -type has been confirmed by simulation studies, indicating that PWM is an effective technique for ensuring capacitor voltage balance throughout all operating areas without requiring additional circuits.

#### **ACKNOWLEDGEMENTS**

The authors gratefully acknowledge the support of time and facilities from Ho Chi Minh city University of Industry and Trade for this study.

#### REFERENCES

- [1] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters State of the art, challenges, and requirements in Industrial applications," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- [2] S. Kouro et al., "Recent advances and industrial applications of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [3] I. Harbi et al., "Common dc-link multilevel converters: topologies, control and industrial applications," *IEEE Open Journal of Power Electronics*, vol. 4, pp. 512–538, 2023.

- [4] S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," *IET Power Electronics*, vol. 4, no. 4, pp. 384–392, Apr. 2011.

- [5] X. Zhang, T. Zhao, W. Mao, D. Tan, and L. Chang, "Multilevel inverters for grid-connected photovoltaic applications: Examining emerging trends," *IEEE Power Electronics Magazine*, vol. 5, no. 4, pp. 32–41, Dec. 2018.

- [6] A. Bughneda, M. Salem, A. Richelli, D. Ishak, and S. Alatai, "Review of multilevel inverters for PV energy system applications," Mar. 01, 2021, MDPI AG.

- [7] M. Schweizer and J. W. Kolar, "Design and implementation of a highly efficient three-level T-type converter for lowvoltage applications," *IEEE Trans Power Electron*, vol. 28, no. 2, pp. 899–907, 2013.

- [8] X. Yuan, "A four-level π-type converter for low-voltage applications," in 2015 17th European Conference on Power Electronics and Applications, EPE-ECCE Europe 2015, Institute of Electrical and Electronics Engineers Inc., Oct. 2015.

- [9] B. Jin and X. Yuan, "Topology, efficiency analysis, and control of a four-level π -type converter," *IEEE J Emerg Sel Top Power Electron*, vol. 7, no. 2, pp. 1044–1059, Jun. 2019.

- [10] J. Pou, R. Pindado, and D. Boroyevich, "Voltage-balance limits in four-level diode-clamped converters with passive front ends," *IEEE Transactions on Industrial Electronics*, vol. 52, no. 1, pp. 190–196, Feb. 2005.

- [11] M. Saeedifard, R. Iravani, and J. Pou, "Analysis and control of DC-capacitor-voltage-drift phenomenon of a passive front-end five-level converter," *IEEE Transactions on*

- Industrial Electronics, vol. 54, no. 6, pp. 3255-3266, Dec. 2007.

- [12] M. Marchesoni, M. Mazzucchelli, P. Tenca, and P. Darmi-09123 Cagliari -Italy, "An optimal controller for voltage balance and power losses reduction in mpc ac/dc/ac converters," 2000.

- [13] Z. Pan, F. Z. Peng, K. A. Corzine, V. R. Stefanovic, J. M. Leuthen, and S. Gataric, "Voltage balancing control of diode-clamped multilevel rectifier/inverter systems," *IEEE Trans Ind Appl*, vol. 41, no. 6, pp. 1698–1706, Nov. 2005.

- [14] R. Rojas, T. Ohnishi, and T. Suzuki, "PWM control method for a four-level inverter," *IEE Proceedings Electric Power Applications*, vol. 142, no. 6, p. 390, 1995, doi.

- [15] A. A. Boora, A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg, "Voltage-sharing converter to supply single-phase asymmetrical four-level diode-clamped inverter with high power factor loads," *IEEE Trans Power Electron*, vol. 25, no. 10, pp. 2507–2520, 2010.

- [16] K. Wang, Z. Zheng, and Y. Li, "A novel carrier-overlapped pwm method for four-level neutral-point clamped converters," *IEEE Trans Power Electron*, vol. 34, no. 1, pp. 7–12, Jan. 2019.

- [17] K. Wang, Z. Zheng, L. Xu, and Y. Li, "A generalized carrier-overlapped PWM method for neutral-point-clamped multilevel converters," *IEEE Trans Power Electron*, vol. 35, no. 9, pp. 9095–9106, Sep. 2020.